Tabla de Contenidos

ESP8266, Soporte completo a WiFi

El chip ESP8266EX ofrece una solución completa y autónomo para las redes Wi-Fi; que se puede utilizar para alojar la aplicación o para soporta de funciones de red Wi-Fi desde otros procesos de aplicaciones.

El chip ESP8266EX ofrece una solución completa y autónomo para las redes Wi-Fi; que se puede utilizar para alojar la aplicación o para soporta de funciones de red Wi-Fi desde otros procesos de aplicaciones.

Cuando el ESP8266 aloja la aplicación, esta arranca desde una memoria flash externa. Se ha integrado una caché para mejorar el rendimiento del sistema en estas aplicaciones.

Como alternativa, este provee un adaptador de WiFi, el acceso a Internet inalánbrica puede ser proporcionado a cualquier sistema basado en Microcontrolador con una simple conectividad a través de una interfaz de una UART o la interfaz Bridge de CPU AHB.

El ESP8266EX se considera el chip WiFi más integrado de la industria; integra los switch de antena, amplificador de potencia, amplificador receptor de bajo ruido, filtros, los módulos administrador de energía, requiere una circuitería externa mínima, y toda la solución, incluyendo el módulo de front-end, está diseñado para ocupar un mínimo de espacio de PCB.

El ESP8266EX integra también una versión mejorada del procesador de 32 bits, seria Diamante modelo L106 de Tensilica, con una SRAM integrada, además de las funcionalidades WiFi. El ESP8266 frecuentemente se integra con sensores externos y otros dispositivos de aplicaciones específicas a través de sus GPIO; se proporcionan código fuente con ejemplos con el SDK.

Características sofisticadas a nivel de sistema, incluyen una rápida funcionalidades de Sleep/Wake (sueño/vigilia) en el contexto de eficiencia energética VoIP, operación de baja potencia de transmisión radio adaptable, procesamiento avanzado de señales y estimula la cancelación y coexistencia y mitigación de interferencias de características de RF con celulares comunes, bluetooth, DDR, LVDS, LCD.

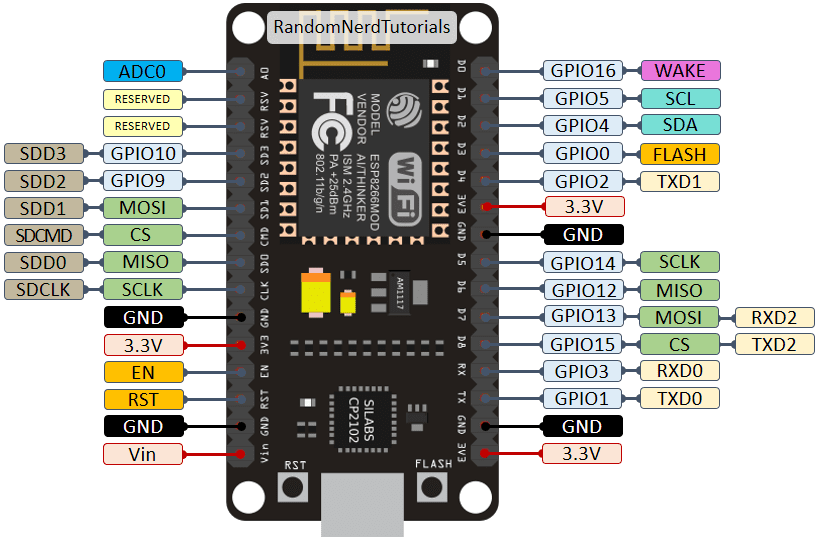

Características Técnicas

- Voltaje de Operación de 5Vdc

- Soc: ESP8266 (Módulo ESP-12)

- Memoria Flash de 4MB o depende del modelo

- Chip USB: CP2102 o CH340G

- 10 Pines de GPIO, puede configurarse como PWM a 3,3Vdc

- 1 Entrada ADC

- 2 UART

- Certificación FCC

- Antena en el PCB

- Protocolo 802.11 b/g/n.

- WiFi directo (P2P), Soft-AP

- Stack del Protocolo TCP/IP integrado.

- Switch TR integrado, balun, LNA, amplificador de potencia y adaptador de red.

- Administración de energía, reguladores y PLL integrado.

- En mode 802.11b salida de potencia de +20.5dBm.

- Soporta una diversidad de Antenas.

- Consumo de Energía en Power-down menor a 10uA.

- MCU de 32 bits integrado de bajo consumo integrada, puede ser utilizado como procesador de aplicaciones.

- STBC, 1×1 MIMO, 2×1 MIMO.

- Incluido A-MPDU & A-MSDU e intervalo de salvado de 0,4uS

- Conección y transmisión de paquetes, menor a 2[ms].

- Consumo de energía en Stanby de < 1mW (DTIM3).

Interfaces del ESP8266

- SDIO 2.0, SPI, UART

- Integra un switch RF, balun, 24dBm PA, DCXO y PMU

- Posee un procesadir RISC, con memoria integrada e interfaz para memoria externa.

- Procesador integrado de MAC/Banda Base para comunicaciones inalámbricas.

- Interfaz I2C para aplicaciones de Audio de Allta Calidad.

- Reguladores de Voltaje “low-dropout” en el chip.

- UART, SPI, SDIO 2.0

- Módulos WEP, TKIP, AES y WAPI integrados.

Tecnología de muy Bajo Consumo

El ESP8266 ha sido diseñado para mobiles, para electrónica de uso en aplicaciones de IoT, con el propósito de lograr el menor consumo de energía con una combinación de varias técnicas propias. La arquitectura de ahorro de energía opera principalmente en 3 modos: el modo activo, modo de reposo y el modo de sueño profundo.

Mediante el uso de avanzadas técnicas de ahorro de energía y la función de la lógica de apagado no son necesarias, y para controlar el cambio entre el sueño y el modo activo, el ESP8266EX consume 60uA en modo de sueño profundo (con el reloj RTC funcionando) y menor a 1.0mA (DTIM=3) o menor a 0,5mA (DTIM=10), aún conectado al Access Point (AP-WiFi).

Cuando está en modo dormido, sólo el reloj calibrado de Tiempo Real (RTC) y el watchdog permanecen activos. El RTC puede ser programado para despertar al ESP8266EX en cualquier momento.

El ESP8266EX puede ser programado para despertar cuando se detecta una condición específica. Esta característica de tiempo mínimo para despertar del ESP8266EX puede ser utilizada por dispositivos móviles SOC's, que les permite permanecer en modo de espera de bajo consumo hasta necesitar WiFi.

Con el fin de satisfacer la demanda de energía de los dispositivos móbiles y electrónicos portátiles, el ESP8266EX puede reducir la salida de potencia del PA( Amplificador de Potencia) para adaptarse a varios perfiles de aplicaciones, mediante la negociación del consumo de energía cuando se está fuera de rango.

Integración con Componentes Externos

Mediante la integración de los componentes más costosos tales como la unidad de administración de energía, switch TR, balun RF, PA de alta potencia capaz de suministrar +25dBm (pico), ESP8266EX asegura que el costo de la lista de materiales es el más bajo posible, y de fácil de integración en cualquier sistema.

Con ESP8266, la única lista de materiales externos son resistencias, condensadores y cristal. Para la compatibilidad del teléfono móvil puede ser necesario un filtro SAW.

Aplicaciones ESP8266EX

- Automatización de Hogares.

- Enchufes inteligentes de Energía.

- Redes en Malla o Mesh Network.

- Sistemas de Control Industrial Wireless.

- Monitoreo de Bebés.

- Cámaras IP.

- Red de Sensores.

- Electrónica de Portátiles.

- Dispositivos de reconocimiento de ubicación por WiFi.

- Etiquetas de Identificación para seguridad.

- Sistemas de Posicionamiento de Balizas de WiFi.

Especificaciones

El siguiente consumo de corriente, se basa en una alimentación de 3.3Vdc a 25ºC, utilizando reguladores internos. Las mediciones se hacen en el puerto de antena sin el filtro SAW. Todas las mediciones del transmisor se basan en el ciclo de trabajo sobre el 90%, en modo de transmisión continua.

| Modo | Típica | Unidad |

|---|---|---|

| Transmisión 802.11b, CCK 1Mbps, Pout=+19.5dBm | 215 | mA |

| Transmisión 802.11b, CCK 11Mbps, Pout=+18.5dBm | 197 | mA |

| Transmisión 802.11g, OFDM, 54Mbps, Pout=+16dBm | 145 | mA |

| Transmisión 802.11n, MCS7, Pout=+14dBm | 135 | mA |

| Recepción 802.11b, largo de paquete de 1024 byte, -80dBm | 60 | mA |

| Recepción 802.11g, largo de paquete de 1024 byte, -70dBm | 60 | mA |

| Recepción 802.11n, largo de paquete de 1024 byte, -65dBm | 62 | mA |

| Stanby | 0.9 | mA |

| Sueño Profundo (RTC) | 60 | uA |

| Modo de ahorro de energía DTIM1 | 1.2 | mA |

| Modo de ahorro de energía DTIM3 | 0.86 | mA |

| Modo Sueño (Retención de Memoria) | 0.31 | mA |

| Apagado Total | 1 | uA |

Sensibilidad del Receptor

Las mediciones siguientes fueron realizadas a temperatura ambiente y con una alimentación de 3,3Vdc y de 1,1Vdc.

| Descripción | Min | Típica | Max | Unidad |

|---|---|---|---|---|

| Frecuencia Entrada | 2412 | 2484 | MHz | |

| Impedancia de Entrada | 50 | Ohms | ||

| Refexión de Entrada | -10 | dB | ||

| Potencia de Salida de PA para 72,2 Mbps | 15.5 | 16.5 | 17.5 | dBm |

| Potencia de Salida de PA para mode 11b | 19.5 | 20.5 | 21.5 | dBm |

| Sensibilidad | ||||

| CCK, 1Mbps | -98 | dBm | ||

| CCK, 11Mbps | -91 | dBm | ||

| 6Mbps (1/2 BPSK) | -93 | dBm | ||

| 54Mbps (3/4 64-QAM) | -75 | dBm | ||

| HT20, MCS7 (65Mbps, 72,2Mbps) | -71 | dBm |

Rechazo de Canales Adjacentes

| Descripción | Min | Típica | Max | Unidad |

|---|---|---|---|---|

| OFDM, 6Mbps | 37 | dB | ||

| OFDM, 54Mbps | 21 | dB | ||

| HT20, MCS0 | 37 | dB | ||

| HT20, MCS7 | 20 | dB |

CPU

Este chip incorpora un Micro de 32 bits de bajo consumo, con un modo de uso de 16 bits. La CPU puede ser interconectada usando:

- Interface iBUS de código para RAM/ROM que va al controlador de memoria, que puede ser usado para accesar la memoria flash externa.

- Interface de memoria de datos dBUS que tambien va al controlador de memoria.

- Interface AHB, para acceso a los registros.

- Interface de JTAG para depuración.

Controlador de Memoria

El controlador de memoria, contiene la ROM y la SRAM. Este es accesado por la CPU , usando las interfaces de iBUS, dBUS y AHB. Cualquiera de estas interfaces puede requerir acceso a los módulos de la ROM o RAM, y el controlador de memoria administra el servicio a estas 3 interfaces, el primero que entra, el primero que se atiende.

AHB y el Bloque AHB

El bloque AHB realiza la función de un árbitro, controla la interfaz AHB desde la MAC, SDIO (host) y CPU. Dependiendo de la dirección, las solicitudes de datos AHB pueden entrar en uno de los dos esclavos:

- Bloque APB

- Controlador Flash (usualmente por aplicaciones standalone o independientes).

Los requerimientos de datos para el controlador de memoria son generalmente requerimientos de alta velocidad, y los requerimientos para el bloque APB son generalmente acceso a los registros.

El bloque de APB actúa como un decodificador. Está destinado solamente para el acceso a los registros programables dentro de los bloques principales del ESP8266. Dependiendo de la dirección, la solicitud del bloque APB puede ir a la radio, SI/SPI, SDIO (host), GPIO, UART, Reloj de Tiempo Real (RTC), MAC o de banda base digital.

Interfaces

El ESP8266EX contiene varias interfaces análogas y digitales que se describen en las siguientes secciones:

Master Control SI/SPI (Opcional)

El Master Serial Interface SI puede operar en Dos, Tres o Cuatro cables en configuración BUS para controlar EEPROM o otros dispositivos I2C/SPI. Multiples dispositivos I2C con diferentes direcciones son soportados en el bus compartido de 2 cables.

Multiples dispositivos SPI son soportados compartiendo las señales de datos y reloj, usando los pines de GPIO desde software como chips select (CS).

El SPI puede ser utilizado para controlar dispositivos externos, tal como memorias flash seriales, decodificadores de audio, o otros dispositivos esclavos. En el arranque es configurado como un dispositivo con una interfaz Master SPI con tres diferentes pines de habilitación:

* SPI_EN0 * SPI_EN1 * SPI_EN2

Ambos, el Master SPI y Esclavo SPI, son soportados con el último utilizado como interfaz de host.

- SPI_EN0: es usada como una señal de habilitación para una memoria flash serial externa para la descarga de código de parche (patch code) y/o MIB-Data para la banda base en una aplicación embebida. En una aplicación base de computador o host, tanto el código de parche y MIB-Data pueden ser bajados alternativamente a través de la interfaz de host. Este pin es Activo Bajo y debe dejarse abierta si no es usado.

- SPI_EN1: Se utiliza usualmente para una aplicación de usuario, por ejemplo para controlar un decoder externo de audio o un sensor ADC en una aplicación embebida. Este pin es Activo bajo y debe quedar abierto si no se usa.

- SPI_EN2: Usualmente usado para controlar una EEPROM para almacenar datos, como información MIB, MAC address, datos de calibración o para uso general. Este pin es Activo bajo y debe quedar abierto si no se usa.

General Purpose IO (GPIO)

Hay un máximo de 16 pines GPIO. Ellos se pueden asignar a varias funciones por medio del firmware. Cada GPIO se puede configurar con una resistencia interna de pull-up/down, entradas disponibles para muestreo de señales por medio de un Registro Interno manejado por software, la entrada es disparada por un flanco o nivel, genera una interrupción a la CPU, esta entrada que provocó una activación del nivel de interrupción, salida controlada de drenaje abierto (open-drain) o salida push-pull, o output-source desde un registro de software, o una salida PWM-DAC.

Estos pines son multiplexados con otras funciones con las interfaces de host, UART, SI, coexistencia de Bluetooth, etc.

Real Time Clock IO (EXT_LFC)

Si tenemos disponible un cristal de 32.768KHz, se puede conectar al EXT\_LFC. Si no tenemos un cristal disponible en este pin, se utilizará LFC interno. Si un EXT\_LFC esta disponible, la selección de la fuente de LFC, LFC interna o EXT\_LFC se puede hacer por un pin directo o conexión directa.

Contactos IO Digitales (Digital IO Pads)

Los pines digitales de IO son bidireccionales, no inversores y son de tres estados. Incluyen un buffer (driver) de entrada y salida, con entrada de tres estados. Además de esto, para operaciones de bajo consumo, el pin de IO puede ser puesto a un “1” permanente. Por ejemplo, cuando el chip es apagado, todas las señales habilitadas de salida pueden ser mantenidas a nivel bajo.

Opcionalmente, si se solicita, la funcionalidad de retención puede ser integrado en el pin de IO. Cuando el pin de IO, no es manejado por una circuitería interna o externa, la funcionalidad de retención puede ser utilizada para mantener el último estado utilizado.

La funcionalidad de retención introduce alguna realimentación positiva en el pin de contacto. Por lo tanto, el driver externo que maneja en pad debe ser más fuerte que la realimentación positiva. La fuerza requerida de accionamiento debe estar sobre el rango de 5uA.

| Parametro | Simbolo | Min | Max | Unidad |

|---|---|---|---|---|

| Input low Voltage | V(IL) | -0.3 | 0.25 x VIO | V |

| Input high Voltage | V(IH) | 0.75 x VIO | 3.6 | V |

| Input leakage Current | I(IL) | 50 | nA | |

| Output low Voltage | V(OL) | 0.1 x VIO | V | |

| Output high voltage | V(OH) | 0.8 x VIO | V | |

| Input pin Capacitance | C(pad) | 2 | pF | |

| VDDIO | V(IO) | 1.7 | 3.6 | V |

| Maximum Drive Capability | I(max) | 12 | mA | |

| Temperature | T(amb) | -20 | 100 | ºC |

Todos los pines IO digitales están protegidos para sobre voltage con un circuito amortiguador conectado entre el pin y GND. El voltage de amortiguamiento de protección es de 6V y el voltaje mantenido es de 5,8V. Esto proporciona protección de sobre voltaje y ESD. La salida del dispositivo esta protegida para voltajes inversos con diodos.

ADC Analogo

El ESP8266EX también integra un conversor análogo digital de 10 bits. El rango de conversión está entre 0V y 1.0Vdc. Esto es usado típicamente para medir el voltaje de un sensor o el estado de la batería. El ADC no debe ser usado cuando el chip está transmitiendo, ya que la referencia de voltaje del conversor es inesacta.

Firmware & Software Development Kit (SDK)

La aplicación y firmware son ejecutados en el chip sobre la ROM y la SRAM, estas instrucciones son cargadas durante el inicio o reinicio a través de la interfaz SDIO, desde la memoria flash externa.

El firmware implemente las especificaciones TCP/IP, el 802.11 b/g/n/e/i completos, el protocolo WLAN MAC y WiFi especificación. Este soporta, no sólo las operaciones de los servicios básicos (BSS) bajo las funciones de control distribuidas (DCF), si no también las operaciones del grupo P2P compatibles con el último protocolo Wi-Fi P2P. Funciones de bajo nivel del protocolo son manejadas automáticamente por el ESP8266:

- RTS/CTS.

- Reconocimiento o Acknowledge.

- Fragmentación y Desfragmentación.

- Agregación.

- Trama de Encapsulamiento (802.11h/RFC-1042).

- Monitorea automático de Beacon y Scanning

- P2P Wi-Fi direct.

Scanning Pasivo o Activo, así como el procedimiento de busqueda P2P, automáticamente son iniciados por el comando adecuado. La administración de energía es manejada con la mínima interacción del host para minimizar el periodo de servicio activo.

Características

El SDK incluye las siguientes bibliotecas de funciones:

- Soporte para 802.11 b/g/n/d/e/i/k/r.

- Soporte para Wi-Fi directo (P2P).

- Busqueda P2P, Modo dueño grupo P2P, Administración de Energía P2P.

- Soporta modo de Estación de Infraestructura BSS, Mode P2P, Mode softAP.

- Aceleradores de hardware para CCMP (CBC-MAC, counter mode), TKIP (MIC, RC4), WAPI (SMS4), WEP (RC4), CRC;

- WPA/WPA2 PSK, y drivers WPS.

- Adicional características de seguridad 802.11i como preautenticación y TSN.

- Interface abierta para varios esquemas de autenticación de capas sobre EAP como TLS, PEAP, LEAP, SIM, AKA o especificaciones especificas.

- Soporte para 802.11n (2.4GHz/5GHz).

- Soporta MINO 1×1 y 2×1, STBC, agregación A-MPDU y A-MSDU, 0,4uS de intervalo de seguridad.

- U-APSD ahorro de energía WMM.

- Administrador de multiples colas para utilización completa de priorización de tráfico definido por el estandar 802.11e.

- Certificación y compatibilidad UMA.

- Encapsulamiento de tramas 802.11h/RFC-1042.

- DMA no secuenciales para la descarga óptima de la CPU en las operaciones de transferencia de datos en copia de ceros.

- Selección de diversidad de antenas (administración del hardware por el software).

- Resuelve la combinación de Velocidad y Consumo con la compatibilidad 802.11 adaptador dinámico de energía para la condición actual de conexión para un mínimo de consumo de energía.

- Algoritmo de reserva de frecuencia adaptativa ajusta la velocidad de transmisión óptima y la potencia base de transmisión sobre la SNR actual y la información de pérdida de paquetes.

- Retransmisión y la Respuesta automática en MAC para evitar desechar paquetes en entornos lentos de host.

- Soporte de roaming.

- Arbitraje de tráfico configurable de paquetes (PTA) con un diseño basado en un procesador esclavo dedicado que proporciona una exacta y flexible sincronización con la coexistencia de Bluetooth para una amplia variedad de componentes bluetooth.

- Soporta la coexistencia de una antena simple y doble de bluetooth con la capacidad de recepción simultánea Wi-Fi y Bluetooth.

Administrador de Energía

El chip se puede poner en los siguientes estados:

- OFF (Apagado): El pin CHIP\_PD es low. El RTC es deshabilitado. Todos los registros están borrados.

- DEEP_SLEEP (Sueño Profundo): Sólo el RTC está encendido, el resto del chip está apagado. Recuperación de memoria del RTC puede mantener una básica información de conexión Wi-Fi.

- SLEEP (Dormido): Sólo el RTC está en funcionamiento. El oscilador de cristal es deshabilitado. Cualquier evento de activación (MAC, Host, timer del RTC, interrupciones externas), ponen al chip en estado Despierto.

- WAKEUP (Despierto): En este estado, el sistema pasa de los estados de reposo al estado PWR. El oscilador de cristal y PLL son habilitados.

- ON (Encendido): El clock de alta velocidad está en funcionamiento y enviado a cada bloque habilitado por el Clock Control Register (CCR). Se implementa con el nivel bajo del clock a nivel de bloques, incluyendo la CPU que puede ser apagada con la instrucción WAITI, mientras el resto del sistema está encendido.

Administración del Clock

La alta frecuencia del relo en el ESP8266EX se usa para accionar ambos mezcladores de transmisión y recepción. Este clock es generado desde el oscilador de cristal interno y un cristal externo. La frecuencia del cristal puede estar entre los 26MHz y 52MHz.

Mientras la calibración interna del oscilador de cristal asegura el uso de una amplia gama de cristales, en general, la calidad del cristal es todavía un factor a considerar, para tener un buen rendimiento se requiere un ruido de fase razonable. Cuando el cristal es seleccionado por debajo de lo óptimo y tiene grandes desvíos de frecuencia o un pobre factor Q, el rendimiento máximo y sensibilidad del sistema Wi-Fi se degrada. Por favor refiérase a las notas de aplicación sobre cómo se puede medir el desplazamiento de frecuencia.

| Parámetro | Simbolo | Min | Max | Unidad |

|---|---|---|---|---|

| Frequency | FXO | 26 | 52 | MHz |

| Loading Capacitance | CL | 32 | pF | |

| Motional Capacitance | CM | 2 | 5 | pF |

| Series Resistance | RS | 0 | 65 | Ohms |

| Frequency tolerance | FXO | -15 | 15 | ppm |

| Frequency vs Temperature (-25ºC ~ 75ºC) | FXO, Temp | -15 | 15 | ppm |

Requerimientos de Referencia Externa

Para un generador de reloj externo, se puede usar un rango de frecuencias entre los 26MHz a los 52MHz. Para un buen desempeño de la radio (RF), se esperan para el clock las siguientes características:

| Parámetro | Simbolo | Min | Max | Unidad |

|---|---|---|---|---|

| Clock Apmplitude | V(xo) | 0.2 | 1 | Vpp |

| External Clock Accuracy | F(xo,ext) | -15 | 15 | ppm |

| Phase noise @1KHz offset, 40MHz clock | -120 | dBc/Hz | ||

| Phase noise @10KHz offset, 40MHz clock | -130 | dBc/Hz | ||

| Phase noise @100KHz offset, 40MHz clock | -138 | dBc/Hz |

Radio (RF)

La radio del ESP8266 consiste en los siguientes bloques principales:

- Receptor de 2.4GHz

- Transmisor de 2.4GHz

- Oscilador de Cristal y generador de reloj de alta velocidad.

- Reloj de Tiempo Real.

- Administrador de Energía.

- Bias y reguladores.

Canales de Frecuencia

El transceptor de RF soporta los siguientes canales de acuerdo al estandar IEEE802.11bgn:

| Channel | Frequency MHz | Channel | Frequency MHz |

|---|---|---|---|

| 1 | 2412 | 8 | 2447 |

| 2 | 2417 | 9 | 2452 |

| 3 | 2422 | 10 | 2457 |

| 4 | 2427 | 11 | 2462 |

| 5 | 2432 | 12 | 2467 |

| 6 | 2437 | 13 | 2472 |

| 7 | 2442 | 14 | 2484 |

Receptor de 2.4GHz

El receptor de 2.4GHz convierte la señal de RF a señales de banda base en cuadratura y los convierte a digital con dos conversores ADC de alta velocidad y alte resolución. Para adaptarse a la variedad de señales, condiciones de canal, filtros de RF, Control de Ganacia automática, circuitos de cancelación de offset y filtros de bandabase son integrados dentro del ESP8266EX.

Transmisor de 2.4GHz

El transmisor que sube a 2,4GHz la señal de cuadratura de Bandabase, y los drive de antena con amplificadores de potencia con CMOS de alta potencia. El uso de calibración digital mejora aún más la linealidad del amplificador de potencia, habilitando un estado del arte de rendimiento de la entrega de potencia media de +20.5dBm para la transmisión de 802.11b y de +16dBm para transmisión de 802.11n.

Adicionalmente se integran calibraciones para cancelar cualquier imperfección de RF, tal como:

- Perdida de portadora

- Comparación de fase I/Q

- Desalineamiento de frecuencia base

Esto reduce la cantidad de tiempo necesario y el equipo de ensayo requerida para las pruebas de producción.

Generador de Clock

El generador de Clock genera cuadraturas de señal de reloj de 2.4GHz para el receptor y transmosor.

Todos los componentes del generador del reloj son integrados en el chip, incluyendo:

- Inductor.

- Varactor.

- Filtro loop.

El generador de reloj incluye una calibración y circuitos de auto chequeo. Las cuadraturas de fases y el ruido de fase son optimizados en el chip con algoritmos de calibración patentados para asegurar el mejor rendimiento de transmisión y recepción.

Velocidades del Protocolo 802.11

El estándar IEEE 802.11 define el uso de los dos niveles inferiores de la arquitectura o modelo OSI (capa física y capa de enlace de datos), especificando sus normas de funcionamiento en una red de área local inalámbrica (WLAN).

Los protocolos de la rama 802.x definen la tecnología de redes de área local (LAN) y redes de área metropolitana (MAN).

| Protocolo IEEE | Banda | Mbps | Protocolo IEEE | Banda | Mbps |

|---|---|---|---|---|---|

| 802.11 Legacy | 2.4GHz | 1 a 2 | 802.11g | 2.4GHz | 54 |

| 802.11a | 5GHz | 20 | 802.11h | 5GHz | 20 |

| 802.11b | 2.4GHz | 5,9 | 802.11n | 2.4GHz - 5GHz | 80 - 100 |